【

儀表網 研發快訊】真空溝道電子器件采用真空縫隙作為器件溝道,其電子遷移率優于所有半導體器件,可滿足高頻通信、高保真模擬電路以及在高溫、強輻射等極端環境下的應用需求。近年來,真空溝道電子器件成為后摩爾基礎元器件的研究熱點。然而,現有真空溝道電子器件多采用電子束光刻、離子束聚焦刻蝕等方法加工其納米溝道,與 CMOS 工藝兼容性差,難以實現大規模制備和應用。

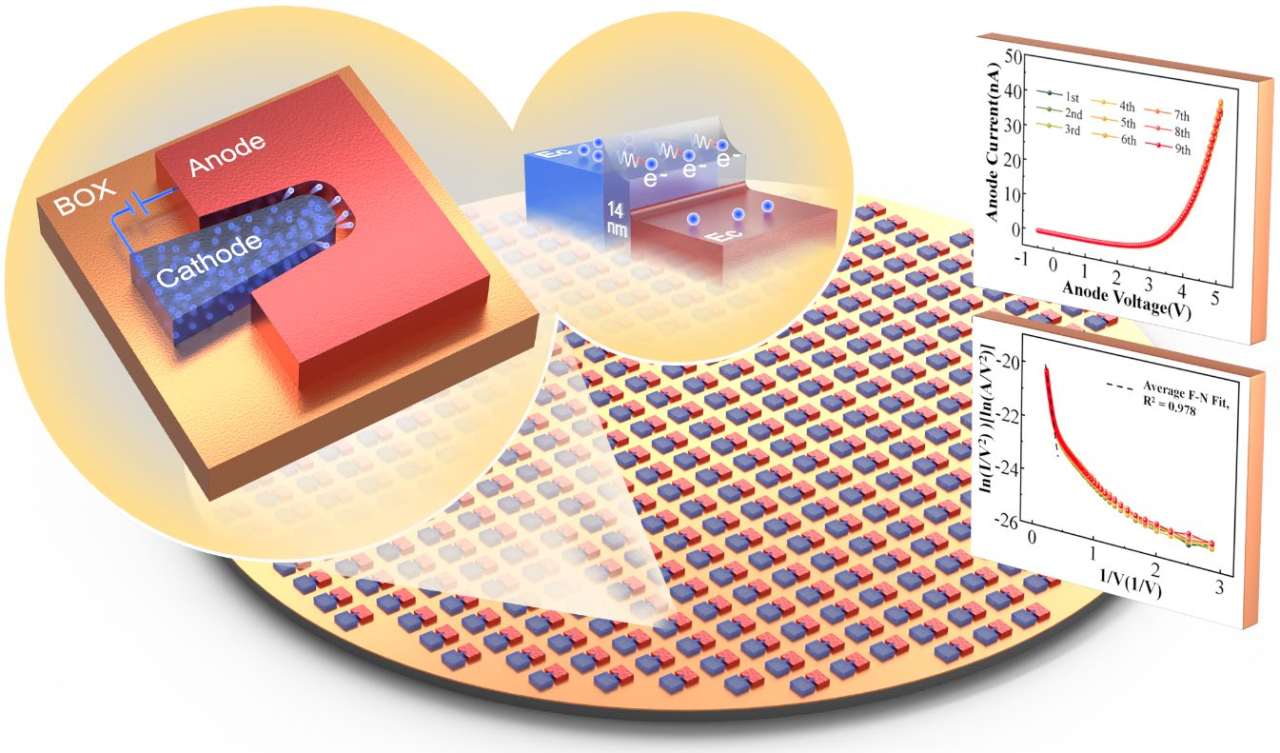

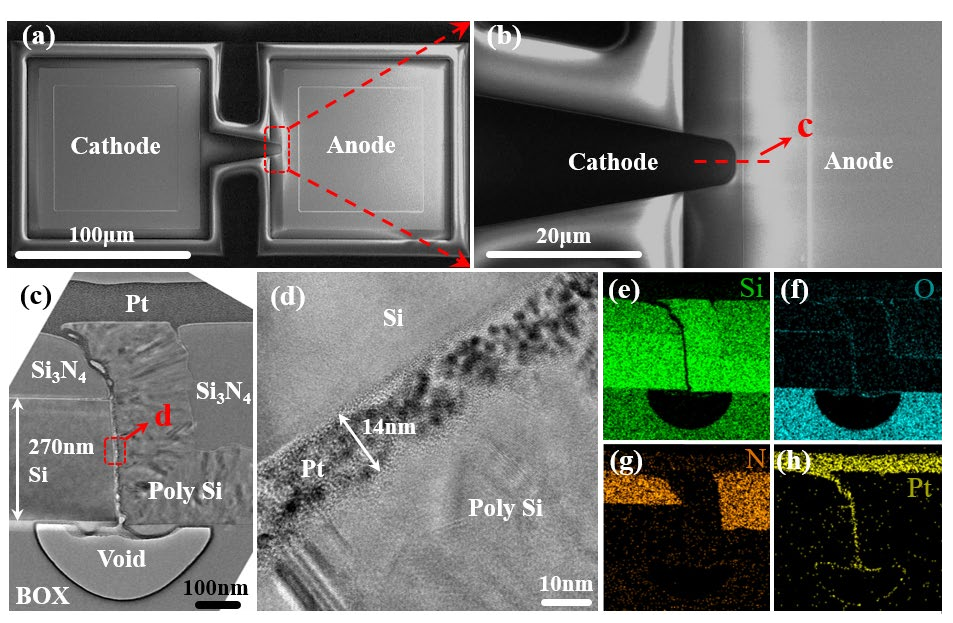

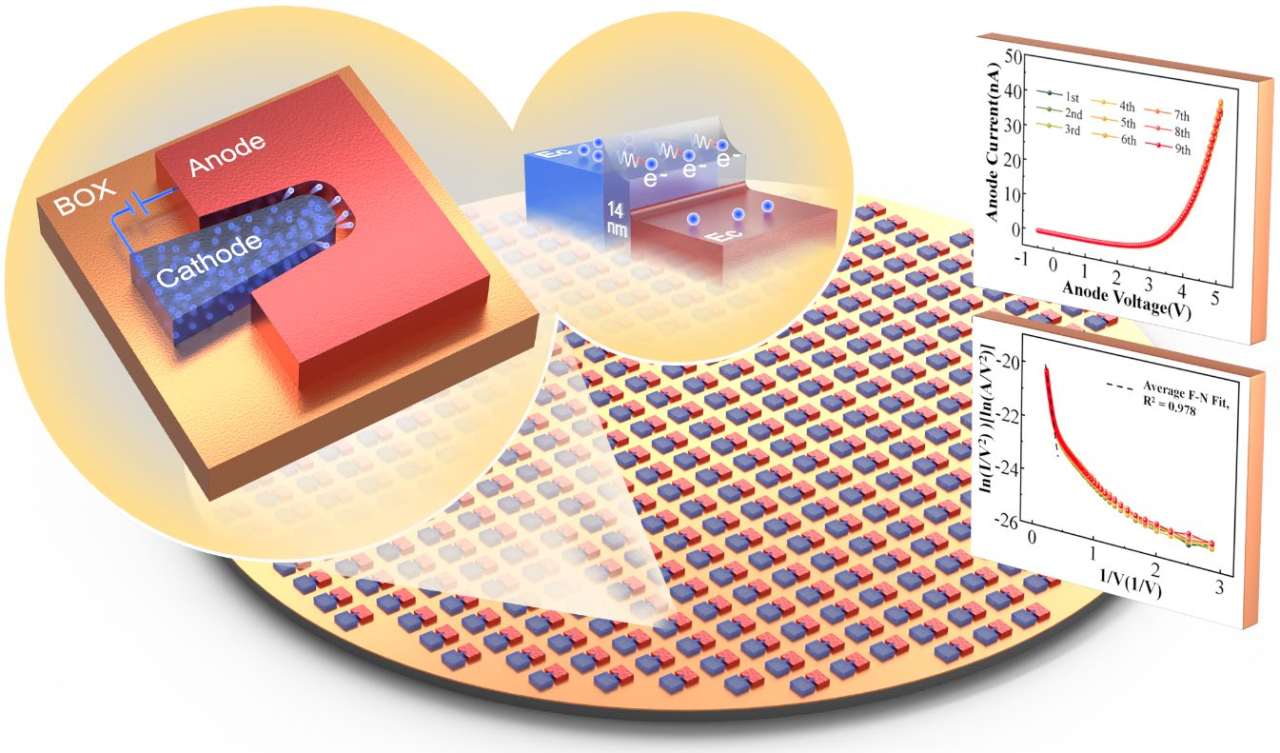

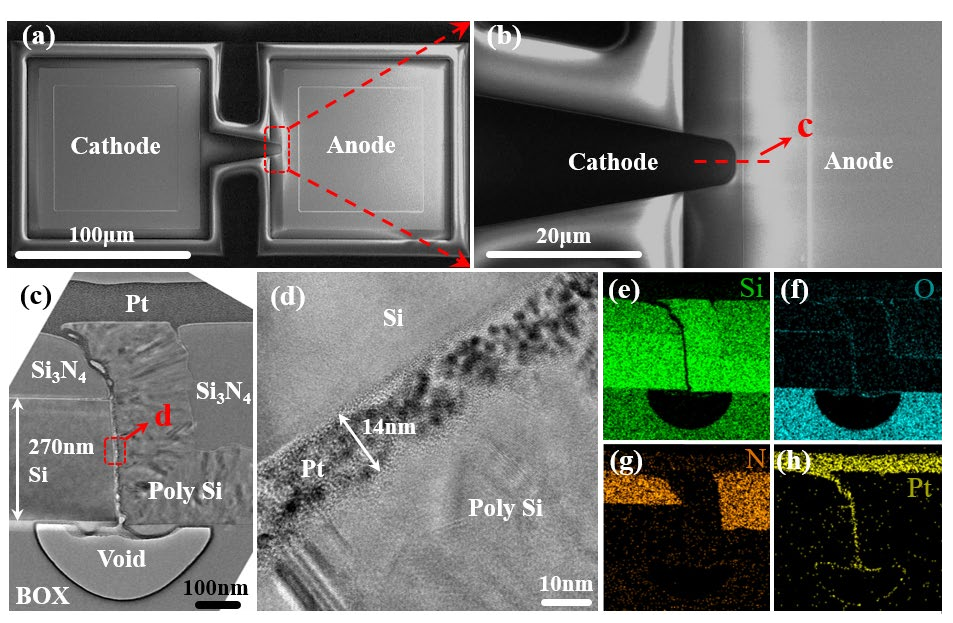

近日,中國科學院上海微系統與信息技術研究所集成電路材料全國重點實驗室俞文杰課題組提出了一種結合化學機械拋光(CMP)及選擇性濕法腐蝕性的新型真空溝道電子器件集成方案。基于SOI襯底材料,該研究團隊成功制備了具有14 nm真空溝道的原型器件,該器件實現了較低開啟電壓(1.8 V)和較高發射電流(70nA@5V,T=300K)。本工作還綜合分析了器件的時間穩定性、溫度響應特性等。該方案與 CMOS 工藝完全兼容,其具有工藝簡單、可控性高、可拓展性強等優勢,對真空溝道電子器件的大規模制造有重要的參考意義。

相關論文以 “ A Novel Approach for Large-Scale Fabrication of Nanoscale Vacuum Electronic Devices with High Compatibility and Controllability”為題,以編輯精選文章(Editors’ Picks)發表于電子器件領域權威期刊《 IEEE Electron Device Letters》。中國科學院上海微系統所博士研究生陳錦和劉強助理研究員為該論文共同第一作者,劉強助理研究員和俞文杰研究員為該論文通訊作者。相關工作得到國家自然科學基金青年科學基金項目(C 類) [原青年科學基金項目]、上海市啟明星揚帆計劃等項目資金支持。

圖 1 真空溝道電子器件示意圖及其電子發射性能

圖 2 真空溝道電子器件微納結構

所有評論僅代表網友意見,與本站立場無關。